**Student Name:**

Solutions

Instuctor: Mustafa Altun

Student ID:

Date: 25/11/2016

## BLG231E Digital Circuits Quiz 2

Duration: 20 Minutes

Grading: 1a) 50%, 1b) 50%,

Quiz is in closed-notes and closed-books format

For your answers please use the space provided in the exam sheet

GOOD LUCK!

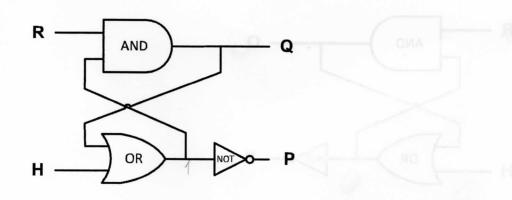

1. Consider a sequential circuit shown below.

a) An expected operation of the circuit is having complemented logic values for Q and P outputs. Determine the restrictions on R and H so that P equals to Q. Fill in the truth table below with indicating the bad conditions or restricted cases

| R | Н | Q-pre | 1QP |                      |

|---|---|-------|-----|----------------------|

| 0 | 0 | 0     | 01  |                      |

| 0 | 0 | 1     | 01  |                      |

| 0 | 1 | 0     | 00  | Same => restricted   |

| 0 | 1 | 1     | 0 6 | ) due = 1 1521119 CO |

| 1 | 0 | 0     | 0 1 |                      |

| 1 | 0 | 1     | 10  |                      |

| 1 | 1 | 0     | 10  |                      |

| 1 | 1 | 1     | 10  |                      |

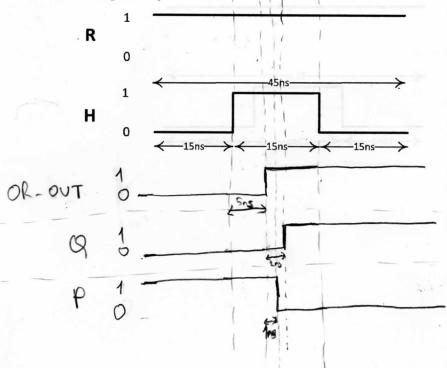

b) Suppose that the inverter has a delay of 1ns; the AND gates has a delay of 2ns; and the OR gate has a delay of 5ns. Sketch the waveforms at the outputs Q and P if the input signals R and H shown below are applied. Suppose that initial values of Q and P are logic 0 and 1, respectively.