Main Page

| (191 intermediate revisions by 2 users not shown) | |||

| Line 1: | Line 1: | ||

| + | __NOTOC__ | ||

<!-- Welcome --> | <!-- Welcome --> | ||

{| id=portal cellspacing="0" cellpadding="0" width=100% style="border:1px solid #B8C7D9; padding:0px;" | {| id=portal cellspacing="0" cellpadding="0" width=100% style="border:1px solid #B8C7D9; padding:0px;" | ||

| Line 4: | Line 5: | ||

| colspan="2" style="background:#CEDFF2; text-align:center; padding:1px; border-bottom:1px #B8C7D9 solid;" | | | colspan="2" style="background:#CEDFF2; text-align:center; padding:1px; border-bottom:1px #B8C7D9 solid;" | | ||

<h2 style="margin:.5em; margin-top:.1em; border-bottom:1px; font-weight:bold;"> | <h2 style="margin:.5em; margin-top:.1em; border-bottom:1px; font-weight:bold;"> | ||

| − | Welcome to the | + | Welcome to the NANOxCOMP Project</h2> |

|- | |- | ||

| − | | valign="top" style="padding:8px 8px 0px 8px; background:#f5fffa;" <!--H210 S4 V100--> | | + | | valign="top" style="padding:8px 8px 0px 8px; background:#f5fffa;" <!--H210 S4 V100--> | |

| − | + | Nano-crossbar arrays have emerged as a strong candidate technology to replace CMOS in near future. They are regular and dense structures, and fabricated by exploiting self-assembly as opposed to purely using lithography based conventional and relatively costly CMOS fabrication techniques. Currently, nano-crossbar arrays are fabricated such that each crosspoint can be used as a conventional electronic component such as a diode, a FET, or a switch. This is a unique opportunity that allows us to integrate well developed conventional circuit design techniques into nano-crossbar arrays. Motivated by this, we aim to develop a complete synthesis and performance optimization methodology for switching nano-crossbar arrays that leads to the design and construction of an emerging nanocomputer. | |

| + | Project objectives are 1) synthesizing Boolean functions with area optimization; 2) achieving fault tolerance; 3) performing performance optimization by considering area, delay, power, and accuracy; 4) implementing arithmetic and memory elements; and 5) realizing a synchronous state machine. | ||

| − | |||

| + | [[Image:Research-nanoarray-1.png|center|none|800px|link=]] | ||

| + | |||

| + | <h2 id="mp-itn-h2" style="margin:0px; width:1010px; background:#F5F5F5; font-size:5%; font-weight:bold; border:0px solid #F5F5F5; text-align:left; color:#000; padding:0em 0em;"> </h2> | ||

|} | |} | ||

| Line 19: | Line 23: | ||

{| id="mp-upper" style="width: 100%; margin:4px 0 0 0; background:none; border-spacing: 0px;" | {| id="mp-upper" style="width: 100%; margin:4px 0 0 0; background:none; border-spacing: 0px;" | ||

<!-- TODAY'S FEATURED ARTICLE; DID YOU KNOW; TODAY'S ARTICLES FOR IMPROVEMENT --> | <!-- TODAY'S FEATURED ARTICLE; DID YOU KNOW; TODAY'S ARTICLES FOR IMPROVEMENT --> | ||

| − | | class="MainPageBG" style="width: | + | | class="MainPageBG" style="width:50%; border:1px solid #B8C7D9; background:#8FBCCF; vertical-align:top; color:#000;" | |

{| id="mp-left" style="width:100%; vertical-align:top; background:#F5F5F5;" | {| id="mp-left" style="width:100%; vertical-align:top; background:#F5F5F5;" | ||

| − | | style="padding:2px;" | <h2 id="mp-tafi-h2" style="margin:3px; background:# | + | | style="padding:2px;" | <h2 id="mp-tafi-h2" style="margin:3px; background:#5F9EA0; font-size:125%; font-weight:bold; border:1px solid #4682B4; text-align:left; color:#000; padding:0.2em 0.4em;">Project details</h2> |

| − | + | {| | |

| + | |- valign=top | ||

| + | | width="140" |'''title''': | ||

| + | | width="500"|Synthesis and Performance Optimization of a Switching Nano-Crossbar Computer | ||

| + | |- valign="top" | ||

| + | | width="140" |'''acronym''': | ||

| + | | width="500"|NANOxCOMP | ||

| + | |- valign="top" | ||

| + | | '''principal investigator / coordinator''': | ||

| + | | [http://www.ecc.itu.edu.tr/index.php?title=Mustafa_Altun Mustafa Altun], [http://www.ecc.itu.edu.tr/index.php?title=Main_Page ECC Group, Istanbul Technical University] | ||

| + | |- valign="top" | ||

| + | | '''partner(s)''': | ||

| + | | width="500"| | ||

| + | * Dr. Dan Alexandrescu, [http://www.iroctech.com/ IROC Techonogies], France <br> | ||

| + | * Prof. Lorena Anghel, [http://tima.imag.fr/tima/en/index.html TIMA Lab.], France (''partnership terminated'')<br> | ||

| + | * Prof. Valentina Ciriani, [http://alos.di.unimi.it/ ALOS Lab., University of Milan], Italy. <br> | ||

| + | * Prof. Csaba A. Moritz, [http://www.umass.edu/nanofabrics/ Nanoscale Computing Fabrics Lab., University of Massachusetts], USA <br> | ||

| + | * Prof. Kaushik Roy, [http://engineering.purdue.edu/NRL/index.html Nanoelectronics Research Lab., Purdue University], USA <br> | ||

| + | * Prof. Georgios Sirakoulis, [http://www.ee.duth.gr/en/ Department of Electrical and Computer Engineering, Democritus University of Thrace], Greece (''new partner'') <br> | ||

| + | * Prof. Mircea Stan, [http://hplp.ece.virginia.edu/home High-Performance Low-Power Lab., University of Virginia], USA <br> | ||

| + | * Prof. Mehdi B. Tahoori, [http://cdnc.itec.kit.edu/index.php Dependable Nano-Computing Group, Karlsruhe Institute of Technology], Germany | ||

| − | + | |- valign="top" | |

| + | | '''funding agency & program''': | ||

| + | | width="500"| [http://ec.europa.eu/research/mariecurieactions/about-msca/actions/rise/index_en.htm European Union/European Commission H2020 MSCA Research and Innovation Staff Exchange Program (RISE)] <br> [http://www.youtube.com/watch?v=dVeJFeKYrLs&feature=youtu.be RISE Video] | ||

| + | |- valign="top" | ||

| + | | '''budget''': | ||

| + | | 724.500 EURO | ||

| + | |- valign="top" | ||

| + | | '''duration''': | ||

| + | | 2015-2019 | ||

| + | |} | ||

| − | |||

| − | + | {| style="margin-left: auto; margin-right: auto; border:1px solid #abd5f5; background:#CEDFE0; padding:0.2em 0.5em;" | |

| − | + | |- valign=top | |

| + | | |'''This project''' | ||

| + | * gathers globally leading research groups working on nanoelectronics and EDA; | ||

| + | * targets variety of emerging technologies including nanowire/nanotube crossbar arrays, magnetic switch-based structures, and crossbar memories; and | ||

| + | * contributes to the construction of emerging computers beyond CMOS by proposing nano-crossbar based computer architectures. | ||

| + | [[Image:nanoxcomp_logo.png|center|none|300px|link=]] | ||

| − | |||

| − | |||

| − | + | [[Image:nanoxcomp_partners.png|center|none|450px|link=]] | |

| − | + | |} | |

| − | + | ||

| − | + | ||

| − | + | ||

| + | {|BORDER=0> | ||

| + | |- | ||

| + | <div><center> | ||

| + | |||

| + | |||

| + | '''PRESENTATIONS''' | ||

| + | <li style="display: inline-block;"> | ||

| + | <span class="plainlinks"> | ||

| + | |||

| + | [[File:PPT.jpg|70px|link=http://www.ecc.itu.edu.tr/images/5/57/NANOxCOMP_DATE16_slides_2016.pptx]] | ||

| + | </span> | ||

| + | <br> [http://www.ecc.itu.edu.tr/images/5/57/NANOxCOMP_DATE16_slides_2016.pptx Slides] | ||

| + | |||

| + | <li style="display: inline-block;"> <span style="color:#f1f5fc"> SPACE</span> | ||

| + | |||

| + | <li style="display: inline-block;"> | ||

| + | <span class="plainlinks"> | ||

| + | |||

| + | [[File:PDF.png|70px|link=http://www.ecc.itu.edu.tr/images/2/29/NANOxCOMP_DATE16_poster_2016.pdf]] | ||

| + | </span> | ||

| + | <br> [[Media:NANOxCOMP_DATE16_poster_2016.pdf | Poster]] | ||

| + | |||

| + | <li style="display: inline-block;"> <span style="color:#f1f5fc"> SPACE</span> | ||

| + | |||

| + | <li style="display: inline-block;"> | ||

| + | <span class="plainlinks"> | ||

| + | |||

| + | [[File:VIDEO.png|70px|link=http://www.youtube.com/watch?v=iwMSSvE1y8s&feature=youtu.be]] | ||

| + | </span> | ||

| + | <br> [http://www.youtube.com/watch?v=iwMSSvE1y8s&feature=youtu.be Video] | ||

| + | |||

| + | </center></div> | ||

|} | |} | ||

| + | |||

| + | |} | ||

| + | |||

| + | ---- | ||

| + | <!-- <div style="margin-left:0.8em;">If interested, please contact [[Mustafa_Altun|Mustafa]]: | ||

| + | * '''email:''' altunmus@itu.edu.tr | ||

| + | * '''office:''' EEF 3005 (coffee guaranteed)</div> --> | ||

| + | <div style="margin-left:0.8em;"> This project has received funding from the European Union's H2020 research and innovation programme under the Marie Skłodowska-Curie grant agreement No 691178. | ||

| + | |||

| style="border:1px solid transparent;" | | | style="border:1px solid transparent;" | | ||

<!-- Interested in joining our group? --> | <!-- Interested in joining our group? --> | ||

| − | | class="MainPageBG" style="width: | + | | class="MainPageBG" style="width:50%; border:1px solid #BA55D3; background:#F8F8FF; vertical-align:top;"| |

{| id="mp-right" style="width:100%; vertical-align:top; background:#F8F8FF;" | {| id="mp-right" style="width:100%; vertical-align:top; background:#F8F8FF;" | ||

| − | | style="padding:2px;" | | + | | style="padding:2px;" | |

| − | < | + | <h2 id="mp-itn-h2" style="margin:3px; background:#BC8F8F; font-size:125%; font-weight:bold; border:1px solid #BA55D3; text-align:left; color:#000; padding:0.2em 0.4em;">Project by the numbers, 2015-2019 </h2> |

| − | + | Started in 2015, the project has been successfully completed in 2019 with many achievements including: | |

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | * | + | * <span style="background:#F5F5F5; font-size: 125%; border:2px solid #B22222;"> 34</span> researchers have been seconded to project partners, performing a total of <span style="background:#F5F5F5; font-size: 125%; border:2px solid #B22222;"> 110,93</span> secondment months. <span style="background:#F5F5F5; font-size: 125%; border:2px solid #B22222;"> 17</span> of them are early stage researchers and <span style="background:#F5F5F5; font-size: 125%; border:2px solid #B22222;"> 9</span> of them are female researchers. |

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | * <span style="background:#F5F5F5; font-size: 125%; border:2px solid #B22222;"> 32</span> peer-reviewed papers contributed by 30 project secondees or partners have been published. <span style="background:#F5F5F5; font-size: 125%; border:2px solid #B22222;"> 12</span> of them are journal papers. | |

| − | < | + | |

| − | + | * <span style="background:#F5F5F5; font-size: 125%; border:2px solid #B22222;"> 35</span> dissemination, outreach, and management activities have been performed. | |

| − | * | + | |

| − | |||

|} | |} | ||

| − | [[tr:]] | + | <h2 id="mp-itn-h2" style="margin:3px; background:#BC8F8F; font-size:125%; font-weight:bold; border:1px solid #BA55D3; text-align:left; color:#000; padding:0.2em 0.4em;">Project activity news </h2> |

| + | |||

| + | * We present our work "''Nano-Crossbar based Computing: Lessons Learned and Future Directions''" in a premier conference on electronic design automation [http://www.date-conference.com/ DATE 2020]. | ||

| + | |||

| + | * We present our work "''CMOS Implementation of Switching Lattices''" in a premier conference on electronic design automation [http://www.date-conference.com/ DATE 2020]. | ||

| + | |||

| + | * We present our work "''Analog Neural Network based on Memristor Crossbar Arrays''" in [http://www.eleco.org.tr/ ELECO 2019]. | ||

| + | |||

| + | * We present our work "''Noise-induced Performance Enhancement of Variability-aware Memristor Networks''" in [http://www.ieee-icecs2019.org/ ICECS 2019]. | ||

| + | |||

| + | * We give a keynote talk "''Computing with Nano-crossbar Arrays''" in [http://www.iaria.org/conferences2019/CENICS19.html CENICS 2019]. | ||

| + | |||

| + | * We present our work "''Testability of Switching Lattices in the Cellular Fault Model''" in [http://dsd-seaa2019.csd.auth.gr/ DSD 2019]. | ||

| + | |||

| + | * A new partner Prof. Georgios Sirakoulis from Democritus University of Thrace, Greece has joined our consortium. Welcome! | ||

| + | |||

| + | * We present our work "''Realization of Four-Terminal Switching Lattices: Technology Development and Circuit Modeling''" in a premier conference on electronic design automation [http://www.date-conference.com/ DATE 2019]. | ||

| + | |||

| + | * We present our work "''A Satisfiability-Based Approximate Algorithm for Logic Synthesis Using Switching Lattices''" in a premier conference on electronic design automation [http://www.date-conference.com/ DATE 2019]. | ||

| + | |||

| + | * We present our work "''Fault Mitigation of Switching Lattices under the Stuck-At-Fault Model''" in [http://tima.univ-grenoble-alpes.fr/conferences/lats/2019/ LATS 2019]. | ||

| + | |||

| + | * We present our work "''Testability of Switching Lattices in the Stuck at Fault Model''" in [http://vlsi-soc.di.univr.it/ VLSI-Soc 2018]. | ||

| + | |||

| + | * We present our work "''Integrated Synthesis Methodology for Crossbar Arrays''" in a leading conference on nanocircuits/nanoarchitectures [http://www.nanoarch.org IEEE/ACM-NANOARCH 2018]. | ||

| + | |||

| + | * We showcase our project in a [http://youtu.be/iwMSSvE1y8s YouTube video]. | ||

| + | |||

| + | * We present our work "''Logic Synthesis and Defect Tolerance for Memristive Crossbar Arrays''" in a premier conference on electronic design automation [http://www.date-conference.com/ DATE 2018]. | ||

| + | |||

| + | * We present our work "''Yield Analysis of Nano-Crossbar Arrays for Uniform and Clustered Defect Distributions''" in [http://icecs2017.org/ IEEE-ICECS 2017]. | ||

| + | |||

| + | * We publicly introduce our project in [http://www.english.sci-all.com/ Science Unites All (SCI-ALL) 2017] - [http://ec.europa.eu/research/mariecurieactions/about/researchers-night_en European Researchers' Night Event]. | ||

| + | <!-- * Our two papers in the area of ''fault tolerance for nano-crossbar arrays'' are accepted in journals [http://csur.acm.org/ CSUR] and [http://ieeexplore.ieee.org/xpl/RecentIssue.jsp?punumber=6245516 TETC] having impact factors of 6,8 and 3,8. This endorses our leading expertise in this area. --> | ||

| + | |||

| + | * We present our work "''Composition of Switching Lattices and Autosymmetric Boolean Function Synthesis''" in [http://dsd-seaa2017.ocg.at/dsd2017 DSD 2017]. | ||

| + | |||

| + | * We present our work "''Spintronic Memristor based Offset Cancellation Technique for Sense Amplifiers''" in [http://smacd2017.unisa.it/ SMACD 2017]. | ||

| + | |||

| + | * We successfully have our midterm review meeting in Lausanne, Switzerland on March 2017. For the agenda [[Media:1-691178-NANOxCOMP-MTM-agenda.pdf | click here]]. | ||

| + | |||

| + | * We present our work "''Computing with Nano-Crossbar Arrays: Logic Synthesis and Fault Tolerance''" in a premier conference on electronic design automation [http://www.date-conference.com/ DATE 2017]. | ||

| + | <!-- | ||

| + | * Our paper is accepted in a leading journal in design automation [http://ieeexplore.ieee.org/xpl/RecentIssue.jsp?punumber=43 IEEE TCAD]. --> | ||

| + | |||

| + | * We present our work "''Synthesis on Switching Lattices of Dimension-Reducible Boolean Functions''" in [http://ati.ttu.ee/vlsi-soc2016/ VLSI-Soc 2016]. | ||

| + | |||

| + | * We present our project and our work on ''logic synthesis of switching nanoarrays'' in [http://dsd-seaa2016.cs.ucy.ac.cy/index.php?p=DSD2016 DSD 2016]. | ||

| + | |||

| + | * We give an invited talk "''EU H2020 Success Story''" in [http://msca-association.teamwork.fr/en/programme H2020 MSCA 2016 Istanbul Training & Info Event]. | ||

| + | |||

| + | * We present our work "''Power-Delay-Area Performance Modeling and Analysis for Nano-Crossbar Arrays''" in [http://www.isvlsi.org/ IEEE-ISVLSI 2016]. | ||

| + | |||

| + | * We organize [http://sintesilogica.di.unimi.it/ the National Workshop on Logic Synthesis, July 2016] with introducing our project and preliminary research results. | ||

| + | |||

| + | * We give an invited talk "''Circuit Design and Optimization of Nano-Crossbar Arrays''" in [http://www.nanotr12.org/ NanoTR-12]. | ||

| + | |||

| + | * We give a plenary talk "''Implementation of a Switching Nano-Crossbar Computer''" in [http://www.wseas.org/cms.action?id=11327 ACS 2016]. | ||

| + | |||

| + | * We present and exhibit our ''EU H2020 project NANOxCOMP'' in a premier conference on electronic design automation [http://www.date-conference.com/ DATE 2016] with over 1000 attendees from academia and industry. | ||

| + | <!-- | ||

| + | * We publish a book chapter "''Computing with Emerging Nanotechnologies''" in a book [http://link.springer.com/book/10.1007/978-3-319-25340-4 "Low-Dimensional and Nanostructured Materials and Devices"]. --> | ||

| + | |||

| + | |||

| + | [[Image:nanoxcomp_logo.png|center|none|300px|link=]] | ||

| + | |||

| + | <!-- | ||

| + | ---- | ||

| + | <div style="margin-left:0.8em;">If interested, please contact [[Mustafa_Altun|Mustafa]]: | ||

| + | * '''email:''' altunmus@itu.edu.tr | ||

| + | * '''office:''' EEF 3005 (coffee guaranteed)</div> - | ||

| + | <div style="margin-left:0.8em;"> This project has received funding from the European Union's H2020 research and innovation programme under the Marie Skłodowska-Curie grant agreement No 691178.-> | ||

| + | |} | ||

| + | |} | ||

Latest revision as of 17:25, 7 May 2020

Welcome to the NANOxCOMP Project | |

|

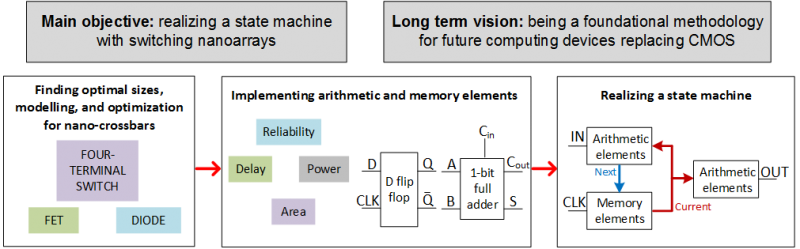

Nano-crossbar arrays have emerged as a strong candidate technology to replace CMOS in near future. They are regular and dense structures, and fabricated by exploiting self-assembly as opposed to purely using lithography based conventional and relatively costly CMOS fabrication techniques. Currently, nano-crossbar arrays are fabricated such that each crosspoint can be used as a conventional electronic component such as a diode, a FET, or a switch. This is a unique opportunity that allows us to integrate well developed conventional circuit design techniques into nano-crossbar arrays. Motivated by this, we aim to develop a complete synthesis and performance optimization methodology for switching nano-crossbar arrays that leads to the design and construction of an emerging nanocomputer. Project objectives are 1) synthesizing Boolean functions with area optimization; 2) achieving fault tolerance; 3) performing performance optimization by considering area, delay, power, and accuracy; 4) implementing arithmetic and memory elements; and 5) realizing a synchronous state machine.

| |

This project has received funding from the European Union's H2020 research and innovation programme under the Marie Skłodowska-Curie grant agreement No 691178.

|

|

Project activity news

|