Research

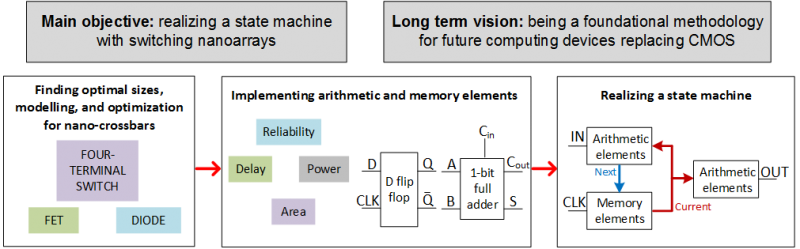

We aim to develop a complete synthesis and performance optimization methodology for switching nano-crossbar arrays that leads to the design and construction of an emerging nanocomputer. Our objectives are 1) synthesizing Boolean functions with area optimization; 2) achieving fault tolerance; 3) performing performance optimization by considering area, delay, power, and accuracy; 4) implementing arithmetic and memory elements; and 5) realizing a synchronous state machine.

Logic Synthesis | |||||||||||||||||||||||||||||||||

|

We study implementation of Boolean functions with nano-crossbar arrays where each crosspoint behaves as a diode, a FET, and a four-terminal switch. For these three types, we give array size formulations for a given Boolean function. Additionally, we focus on four-terminal switch based implementations and propose an algorithm that implements Boolean functions with optimal array sizes.

| |||||||||||||||||||||||||||||||||

|} |}

Fault Tolerance | |||||||||||||||||||||||||||||||

|

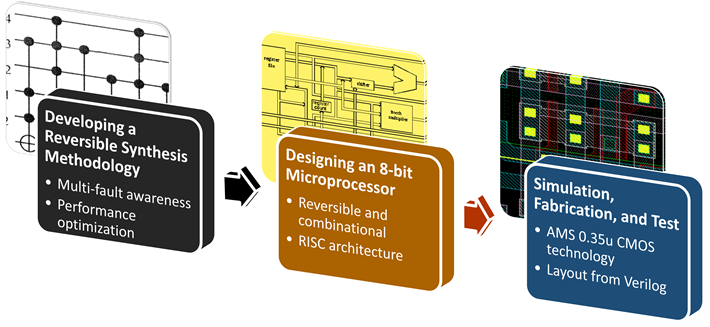

We examine reconfigurable crossbar arrays by considering randomly occurred stuck-open and stuck-closed crosspoint faults. In the presence of permanent faults, a fast and accurate heuristic algorithm is proposed that uses the techniques of index sorting, backtracking, and row matching. In the presence of transient faults, tolerance analysis is performed by formally and recursively determining tolerable fault positions  Synthesis and OptimizationWe propose a fast synthesis algorithm that implements any given reversible Boolean function with quantum gates. Instead of an exhaustive search on every given function, our algorithm creates a library of essential functions and performs sorting. As an example, to implement 4 bit circuits we only use 120 essential functions out of all 20922789888000 functions. We also perform optimization for both reversible and quantum circuit costs by considering adjacent gate pairs.

| |||||||||||||||||||||||||||||||

Performance Modeling and Analysis | |||||||||||||||||||||||||

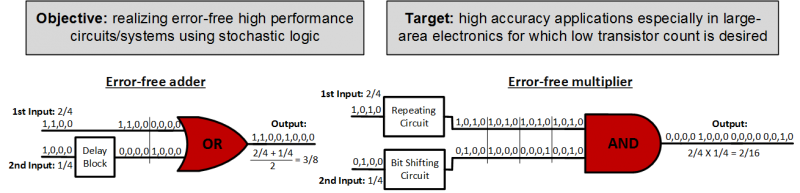

Accurate Arithmetic ImplementationsWe propose a method to overcome the main drawback in stochastic computing, low accuracy or related long computing times. Our method manipulates stochastic bit streams with the aid of feedback mechanisms. We implement error-free arithmetic multiplier and adder circuits by considering performance parameters area, delay, and accuracy.

| |||||||||||||||||||||||||